Researchers at the Massachusetts Institute of Technology (MIT) have developed a new superconducting nanowire memory array that exhibits a significantly lower error rate compared to existing superconducting memories. This breakthrough, detailed in a paper published on January 25, 2026, in the journal Nature Electronics, could pave the way for more efficient memory components in quantum computing systems.

Quantum computers rely on advanced memory technologies to manage the complex tasks they perform. Traditional superconducting memories, while promising, often struggle with error rates and scalability. The new design utilizes one-dimensional nanostructures known as nanowires, which enhance performance and minimize errors, making them more suitable for practical applications.

Advancements in Superconducting Memory Technology

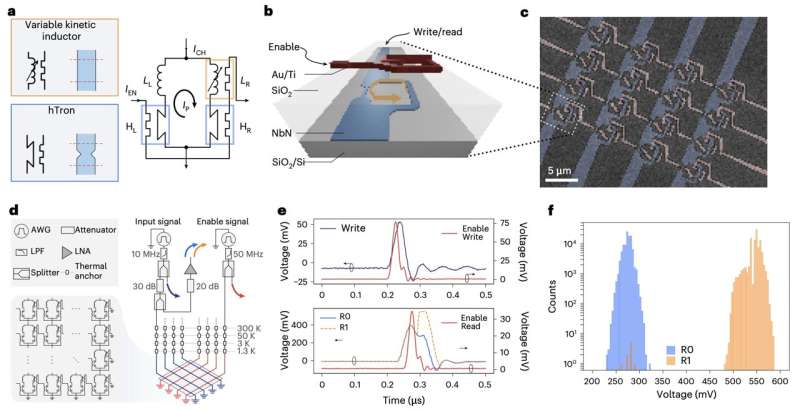

The research team, led by Owen Medeiros and Matteo Castellani, created a compact 4 × 4 superconducting nanowire memory array that operates at 1.3 K. Each memory cell consists of a superconducting nanowire loop, which includes two temperature-dependent superconducting switches and a variable kinetic inductor. This configuration allows the memory to perform stable operations while minimizing bit errors.

Medeiros and his colleagues noted, “Conventional superconducting logic-based memory cells possess a large footprint that limits scaling; nanowire-based superconducting memory cells, although more compact, have high error rates, which hinders integration into large arrays.” Their innovative approach aims to address these challenges, reporting a functional density of 2.6 Mbit cm −2 for their memory array.

The team developed a method for writing and reading information using precisely timed electrical pulses sent to specific memory cells. These pulses momentarily heat one of the nanowire switches, temporarily increasing its resistance and injecting a magnetic flux into the loop, which encodes data values (0 or 1). Once the pulse concludes and the nanowire returns to its superconducting state, the information is securely stored.

Promising Results and Future Applications

Initial tests revealed that the new superconducting memory array achieves a remarkably low bit error rate of approximately 1 in 100,000 operations. This performance is a significant improvement over previous superconducting memory technologies, which typically exhibit much higher error rates. The study found a minimum bit error rate of 10 −5, suggesting that this new memory design could be a crucial component in the development of low-energy superconducting computers and fault-tolerant quantum computers.

The authors emphasized the importance of their findings, stating, “We also use circuit-level simulations to understand the memory cell’s dynamics, performance limits, and stability under varying pulse amplitudes.” This research could lead to further advancements in superconducting memory systems, bringing them closer to reliable deployment in real-world applications.

The progress made by the MIT team signifies a critical step toward developing efficient memory solutions for quantum computing, potentially transforming how data is processed in the future. As researchers continue to refine and scale these designs, the dream of practical, low-error superconducting memory could soon become a reality.